The 22nm is an index of the distance between discrete elements of the die. I think so at least.

Not quite.

The reported "size" at a particular process node (22nm in this case) is the average half-pitch of a single DRAM cell (that's simplifying somewhat, but it works for this discussion). The pitch is often reported to be the "distance between cells". That's not entirely accurate, the way most people think about it, because it assumes that the "cells" themselves take up no space at all. That's not what it means.

The DRAM half-pitch is roughly the size of the average DRAM cell at a particular process node. Despite the fact that they are "manufactured", the cell size does vary from transistor to transistor. Measuring actual transistors isn't easy. Because they are three-dimensional (and infinitesimally small) is difficult tell where the transistor itself begins and ends. However, you can accurately measure the distance across the cells, using the contacts as your "border". One-half of that distance, roughly correlates to the size of the transistor within. Pictures make it clear:

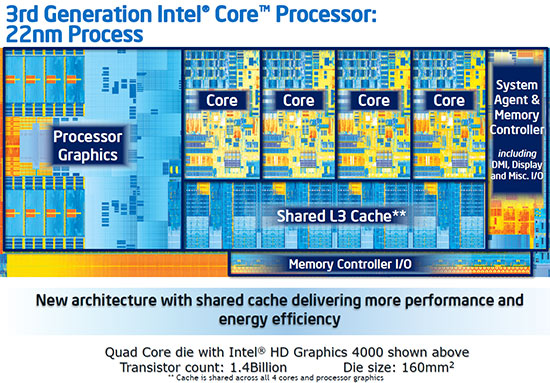

If you look at any modern CPU core under a microscope, you can see that the DRAM cache actually takes up a substantial amount of the surface area of the chip:

See all the "boring-blue" sections in each of the different cores? That's all memory cells, as is the entire L3 cache area.

See all the "boring-blue" sections in each of the different cores? That's all memory cells, as is the entire L3 cache area.Plus, because memory cells are fundamental and relatively simple, that's typically the first thing at any process node that they push out (those ultra-tiny "demos" that IBM and others have shown are all made up of sometimes-functional-sometimes-not DRAM cells, or NAND which is even easier to get down to very small feature sizes). And, different functional units are actually shaped/sized differently, so you can't just say a blanket "our transistors are x size" across an entire complex chip.

So, at any given process node, the "size" given is more of an average feature size. Specifically, it correlates to the DRAM cell size, which is usually the most common transistor on any given chip, but even if not, the lithography process is all the same size, so they other features' sizes correlate to the DRAM cell size.

Make sense?

Author

Topic: What is 22nm technology? (Read 12735 times)

Author

Topic: What is 22nm technology? (Read 12735 times)